# SQFlash Micro SD Card Technical Manual

(SQF-MSDS1-xG-21x)

REV 0.3 Page 1 of 20 Mar. 24, 2019

## **CONTENTS**

| 1. Overview                         | 4  |

|-------------------------------------|----|

| 2. Standard Features                | 5  |

| 3. Additional Features              | 6  |

| 4. Flash Management                 | 8  |

| 5. Pin Assignment and Block Diagram | 9  |

| 6. Power Consumption                | 10 |

| 7. Electrical Specifications        | 10 |

| 8. DC Characters                    | 10 |

| 9. AC Characters                    | 13 |

| 10. Dimensions                      | 18 |

### **Revision History**

| Rev. | Date      | History                     |  |  |  |

|------|-----------|-----------------------------|--|--|--|

| 0.1  | 2017/3/27 | 1. 1 <sup>st</sup> draft    |  |  |  |

| 0.2  | 2018/5/23 | Modify description          |  |  |  |

| 0.3  | 2019/3/24 | Add temperature information |  |  |  |

|      |           |                             |  |  |  |

|      |           |                             |  |  |  |

Advantech reserves the right to make changes without further notice to any products or data herein to improve reliability, function, or design. Information furnished by Advantech is believed to be accurate and reliable. However, Advantech does not assure any liability arising out of the application or use of this information, nor the application or use of any product or circuit described herein, neither does it convey any license under its patent rights nor the rights of others.

Copyright © 1983-2019 Advantech Co., Ltd. All rights reserved.

## 1. Overview

The SQFlash Micro Secure Digital card (SQF-MSD) is fully compliant to the specification released by SD Card Association. The Command List supports [Part 1 Physical Layer Specification Ver3.01 Final] definitions. Card Capacity of Non-secure Area, Secure Area Supports [Part 3 Security Specification Ver3.00 Final] specifications.

The microSD 3.0 card comes with 8-pin interface, designed to operate at a maximum operating frequency of 50MHz. It can alternate communication protocol between the SD mode and SPI mode. It performs data error detection and correction with very low power consumption. Its capacity could be more than 4GB.

SQFlash Industrial Micro SD card is one of the most popular cards today based on its high performance, good reliability and wide compatibility. Not to mention that it's well adapted for hand-held applications in semi-industrial/medical markets already.

REV 0.3 Page 4 of 20 Mar. 24, 2019

## 2. Standard Features

- Support SD system specification version 3.0

- Card capacity of non-secure area and secure area support [Part 3 Security Specification Ver3.0 Final] Specifications

- Support SD SPI mode

- Designed for read-only and read/write cards

- Bus Speed Mode (using 4 parallel data lines)

- Non-UHS-I mode

- Deafult speed mode: 3.3V signaling, frequency up to 25MHz, up to 12.5 MB/sec

- High speed mode: 3.3V signaling, frequency upto 50MHz, up to 25 MB/sec

- The command list supports [Part 1 Physical Layer Specification Ver3.1 Final] definitions

- Copyrights Protection Mechanism

- Compliant with the highest security of SDMI standard

- Support CPRM (Content Protection for Recordable Media) of SD Card

- Card removal during read operation will never harm the content

- Password Protection of cards (optional)

- Write Protect feature using mechanical switch

- Built-in write protection features (permanent and temporary)

- +4KV/-4KV ESD protection in contact pads

- Operation voltage range: 2.7 ~ 3.6V

REV 0.3 Page 5 of 20 Mar. 24, 2019

## 3. Additional Features

### Capacities

SLC type: 128MB, 256MB, 512MB, 1GB, 2GB, 4GB

#### ■ Flash type

24 nm SLC

#### ■ Performance

| Consoity | Mode    | Sequential  |              |  |  |

|----------|---------|-------------|--------------|--|--|

| Capacity | Wiode   | Read (MB/s) | Write (MB/s) |  |  |

| 128MB    | Non-UHS | 16          | 4            |  |  |

| 256MB    | Non-UHS | 16          | 10           |  |  |

| 512MB    | Non-UHS | 16          | 10           |  |  |

| 1GB      | Non-UHS | 18          | 10           |  |  |

| 2GB      | Non-UHS | 20          | 20           |  |  |

| 4GB      | UHS-I   | 50          | 40           |  |  |

#### ■ Temperature Ranges

- Commercial Temperature

- -25 $^{\circ}$ C to 85 $^{\circ}$ C for operating

- -40°C to 85°C for storage

- Industrial Temperature

- -40°C to 85°C for operating

- -40°C to 85°C for storage

#### Mechanical Specification

Shock: 1,500G, Peak / 0.5ms

Vibration: 20G, Peak / 20~2000Hz

Drop: 1.5m free fall

Bending: ≥ 10N, hold 1min / 5times

Torque: 0.15N-m or +/-2.5deg

Salt Spray:

Concentration: 3% NaCl

Temperature: 35<sup>°</sup>C

• Storage for 24 HRS

Waterproof: JIS IPX7 compliance

#### Humidity

Operating Humidity: 5% ~ 93%Non-Operating Humidity: 5% ~ 93%

#### NAND flash Data Retention

- 10 years

#### ■ Endurance

JEDEC defined an endurance rating TBW (TeraByte Written), following by the equation below, for indicating the number of terabytes a flash drive can be written which is a measurement of flash drive's expected lifespan, represents the amount of data written to the device.

### TBW = [(NAND Endurance) x (Flash Drive Capacity)] / WAF

• NAND Endurance: Program / Erase cycle of a NAND flash.

SLC: 60,000 cyclesUltra MLC: 20,000 cycles

o MLC: 3,000 cycles

• Flash Drive Capacity: Physical capacity in total of a Flash Drive.

• WAF: Write Amplification Factor (WAF), as the equation shown below, is a numerical value representing the ratio between the amount of data that a flash drive controller needs to write and the amount of data that the host's flash controller writes. A better WAF, which is near to 1, guarantees better endurance and lower frequency of data written to flash memory.

#### WAF = (Lifetime write to flash) / (Lifetime write to host)

The TBW rating for a flash drive shall be derived for and verified under the following workload conditions,

Sequential Write (copy file into card)

• P/E cycles incurred: erase count after writing – erase count before writing

#### SQFlash SD Card TBW

| oonooity | твw        |     |  |  |  |

|----------|------------|-----|--|--|--|

| capacity | WAF        | SLC |  |  |  |

| 128 MB   |            | 7   |  |  |  |

| 256 MB   |            | 14  |  |  |  |

| 512 MB   | 4 00 444 4 | 28  |  |  |  |

| 1 GB     | 1.024414   | 58  |  |  |  |

| 2 GB     |            | 117 |  |  |  |

| 4 GB     |            | 234 |  |  |  |

REV 0.3 Page 7 of 20 Mar. 24, 2019

## 4. Flash Management

#### **■** Error Correction Code (ECC)

Flash memory cells will deteriorate with use, which might generate random bit errors in the stored data. Thus, SQF-MSD applies the BCH ECC algorithm, which can detect and correct errors occur during read process, ensure data been read correctly, as well as protect data from corruption.

#### Wear Leveling

NAND Flash devices can only undergo a limited number of program/erase cycles, and in most cases, the flash media are not used evenly. If some area get updated more frequently than others, the lifetime of the device would be reduced significantly. Thus, Wear Leveling technique is applied to extend the lifespan of NAND Flash by evenly distributing write and erase cycles across the media.

SQF-MSD provides advanced Wear Leveling algorithm, which can efficiently spread out the flash usage through the whole flash media area. Moreover, by implementing both dynamic and static Wear Leveling algorithms, the life expectancy of the NAND Flash is greatly improved.

#### Bad Block Management

Bad blocks are blocks that include one or more invalid bits, and their reliability is not guaranteed. Blocks that are identified and marked as bad by the manufacturer are referred to as "Initial Bad Blocks". Bad blocks that are developed during the lifespan of the flash are named "Later Bad Blocks". SQF-MSD implements an efficient bad block management algorithm to detect the factory-produced bad blocks and manages any bad blocks that appear with use. This practice further prevents data being stored into bad blocks and improves the data reliability.

#### Auto-Read Refresh

Auto-Read Refresh is specifically applied on devices that read data mostly but rarely write data, such as GPS. When blocks are continuously read, then the device cannot activate wear leveling since it can only be applied while writing data. Thus, errors will accumulate and become uncorrectable. Accordingly, to avoid errors exceed the amount ECC can correct and blocks turn bad, The firmware of SQF-MSD will automatically refresh the bit errors when the error number in one block approaches the threshold, ex., 24 bits.

REV 0.3 Page 8 of 20 Mar. 24, 2019

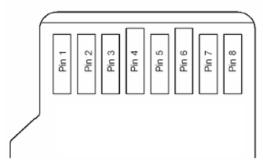

## 5. Pin Assignment and Block Diagram

|     |                      | SD Mode           |                                 |          | SPI Mode |                        |  |  |

|-----|----------------------|-------------------|---------------------------------|----------|----------|------------------------|--|--|

| pin | Name                 | Type <sup>1</sup> | Description                     | Name     | Туре     | Description            |  |  |

| 1   | DAT2                 | I/O/PP            | Data Line[bit2]                 | RSV      |          |                        |  |  |

| 2   | CD/DAT3 <sup>2</sup> | I/O/PP 3          | Card Detect/<br>Data Line[bit3] | CS       |          | Chip Select (neg true) |  |  |

| 3   | CMD                  | PP                | Command/Response                | DI       |          | Data In                |  |  |

| 4   | $V_{DD}$             | S                 | Supply voltage                  | $V_{DD}$ | S        | Supply voltage         |  |  |

| 5   | CLK                  | I                 | Clock                           | SCLK     |          | Clock                  |  |  |

| 6   | $V_{SS}$             | S                 | Supply voltage ground           | $V_{SS}$ | S        | Supply voltage ground  |  |  |

| 7   | DAT0                 | I/O/PP            | Data Line[bit0]                 | DO       | O/PP     | Data Out               |  |  |

| 8   | DAT1                 | I/O/PP            | Data Line[bit1]                 | RSV      |          |                        |  |  |

- (1) S: power supply, I: input; O: output using push-pull drivers; PP:I/O using push-pull driver

- (2) The extended DAT lines (DAT1-DAT3) are input on power up. They start to operate as DAT lines after SET\_BUS\_WIDTH command. The Host shall keep its own DAT1-DAT3 lines in input mode, as well, while they are not used. It is defined so, in order to keep compatibility to MultiMedia Cards.

- (3) At power up this line has a 50KOhm pull up enabled in the card. This resistor serves two functions Card detection and Mode Selection. For Mode Selection, the host can drive the line high or let it be pulled high to select SD mode. If the host wants to select SPI mode it should drive the line low. For Card detection, the host detects that the line is pulled high. This pull-up should be disconnected by the user during regular data transfer period, with SET\_CLR\_CARD\_DETECT (ACMD42) command.

| Name             | Width  | Description                                                                                                                                         |

|------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| CID              | 128bit | Card identification number; card individual number for identification. <b>Mandatory</b>                                                             |

| RCA <sup>1</sup> | 16bit  | Relative card address; local system address of a card, dynamically suggested by the card and approved by the host during initialization.  Mandatory |

| DSR              | 16bit  | Driver Stage Register; to configure the card's output drivers. Optional                                                                             |

| CSD              | 128bit | Card Specific Data; information about the card operation conditions.  Mandatory                                                                     |

| SCR              | 64bit  | SD Configuration Register; information about the SD Memory Card's Special Features capabilities <b>Mandatory</b>                                    |

| OCR              | 32bit  | Operation conditions register. <b>Mandatory.</b>                                                                                                    |

| SSR              | 512bit | SD Status; information about the card proprietary features  Mandatory                                                                               |

| OCR              | 32bit  | Card Status; information about the card status  Mandatory                                                                                           |

Specifications subject to change without notice, contact your sales representatives for the most update information.

REV 0.3 Page 9 of 20 Mar. 24, 2019

## 6. Power Consumption

Table list as below is the power consumption of SQF-MSD card with different type of flash memory.

| Capacity | Flash Structure | Read | Write | Idle |

|----------|-----------------|------|-------|------|

| 128MB    | 128MB x 1       | 400  | 400   | 1    |

| 256MB    | 256MB x 1       | 400  | 400   | 1    |

| 512MB    | 512MB x 1       | 400  | 400   | 1    |

| 1GB      | 512MB x 2       | 400  | 400   | 1    |

| 2GB      | 512MB x 4       | 400  | 400   | 1    |

| 4GB      | 512MB x 8       | 400  | 400   | 1    |

<sup>(1)</sup> Data transfer mode is single channel.

## 7. Electrical Specifications

Absolute Maximum Rating

| Item | Symbol              | Parameter                       | MIN                  | MAX                  | Unit |

|------|---------------------|---------------------------------|----------------------|----------------------|------|

| 1    | $V_{DD}$ - $V_{SS}$ | DC Power Supply                 | -0.3                 | +3.3                 | V    |

| 2    | $V_{IN}$            | Input Voltage                   | V <sub>SS</sub> -0.3 | V <sub>DD</sub> +0.3 | V    |

| 3    | Та                  | Operating Temperature (Gold)    | -25                  | +85                  | °C   |

| 4    | Та                  | Operating Temperature (Diamond) | -40                  | +85                  | °C   |

| 5    | Tst                 | Storage Temperature             | -40                  | +85                  | °C   |

| 6    | $V_{DD}$            | V <sub>DD</sub> Voltage         | 2.7                  | 3.6                  | V    |

## 8. DC Characters

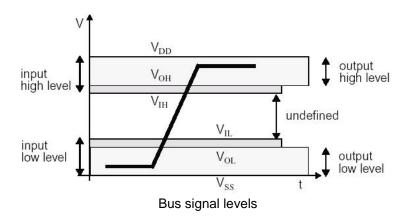

### ■ BUS Operating Conditions for 3.3V Signaling

Threshold level for High Voltage Range

| Parameter           | Symbol | Min       | Max       | Unit | Remarks             |

|---------------------|--------|-----------|-----------|------|---------------------|

| Supply voltage      | VDD    | 2.7       | 3.6       | V    |                     |

| Output High Voltage | VOH    | 0.75*VDD  |           | V    | IOH=-2mA VDDMin.    |

| Output Low Voltage  | VOL    |           | 0.125*VDD | V    | IOL = 2mA VDD min   |

| Input High Voltage  | VIH    | 0.625*VDD | VDD+0.3   | V    |                     |

| Input Low Voltage   | VIL    | VSS-0.3   | 0.25 *VDD | V    |                     |

| Power up time       |        |           | 250       | ms   | from 0v to VDD min. |

REV 0.3 Page 10 of 20 Mar. 24, 2019

| Parameter                 | Symbol | Min      | Max                  | Unit | Remarks |

|---------------------------|--------|----------|----------------------|------|---------|

| Peak voltage on all lines |        | -0.3     | V <sub>DD</sub> +0.3 | V    |         |

| All Inputs                |        | <u> </u> |                      |      |         |

| Input Leakage Current     |        | -10      | 10                   | uA   |         |

| All Outputs               |        |          |                      |      |         |

| Output Leakage Current    |        | -10      | 10                   | uA   |         |

#### ■ Bus Signal Line Levels

| Parameter                                   | symbol                               | Min | Max             | Unit | Remark                                                                  |

|---------------------------------------------|--------------------------------------|-----|-----------------|------|-------------------------------------------------------------------------|

| Pull-up resistance                          | R <sub>CMD</sub><br>R <sub>DAT</sub> | 10  | 100             | kΩ   | to prevent bus floating                                                 |

| Total bus capacitance for each signal line  | C <sub>L</sub>                       |     | 40              | pF   | 1 card<br>C <sub>HOST</sub> +C <sub>BUS</sub> shall<br>not exceed 30 pF |

| Capacitance of the card for each signal pin | C <sub>CARD</sub>                    |     | 10 <sup>1</sup> | pF   |                                                                         |

| Maximum signal line inductance              |                                      |     | 16              | nΗ   | f <sub>pp</sub> <20 MHz                                                 |

| Pull-up resistance inside card (pin1)       | R <sub>DAT3</sub>                    | 10  | 90              | kΩ   | May be used for card detection                                          |

| Capacity Connected to Power Line            | C <sub>C</sub>                       |     | 5               | uF   | To prevent inrush current                                               |

<sup>&</sup>lt;Note 1> This model is SD and eMMC(4.51) controller, so the maximum of eMMC capacitance will be 12pF.

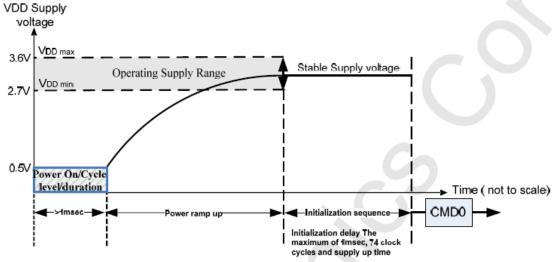

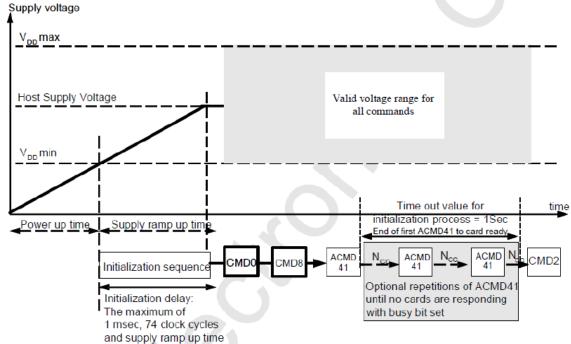

#### **■** Power Up Time of Host

Host needs to keep power line level less than 0.5V and more than 1ms before power ramp up.

Power On or Power Cycle

Followings are requirements for Power on and Power cycle to assure a reliable SD Card hard reset.

Voltage level shall be below 0.5V. Duration shall be at least 1ms.

Power Supply Ramp Up

The power ramp up time is defined from 0.5V threshold level up to the operating supply voltage which is stable between VDD (min.) and VDD (max.) and host can supply SDCLK.

Followings are recommendation of Power ramp up:

Voltage of power ramp up should be monotonic as much as possible.

The minimum ramp up time should be 0.1ms.

The maximum ramp up time should be 35ms for 2.7-3.6V power supply.

Specifications subject to change without notice, contact your sales representatives for the most update information.

Host shall wait until VDD is stable.

After 1ms VDD stable time, host provides at least 74 clocks before issuing the first command. Power Down and Power Cycle

When the host shuts down the power, the card VDD shall be lowered to less than 0.5Volt for a minimum period of 1ms. During power down, DAT, CMD, and CLK should be disconnected or driven to logical 0 by the host to avoid a situation that the operating current is drawn through the signal lines.

If the host needs to change the operating voltage, a power cycle is required. Power cycle means the power is turned off and supplied again. Power cycle is also needed for accessing cards that are already in Inactive State. To create a power cycle the host shall follow the power down description before power up the card (i.e. the card VDD shall be once lowered to less than 0.5Volt for a minimum period of 1ms).

### ■ Power Up Time of Card

A device shall be ready to accept the first command within 1ms from detecting VDD min. Device may use up to 74 clocks for preparation before receiving the first command.

REV 0.3 Page 12 of 20 Mar. 24, 2019

## 9. AC Characters

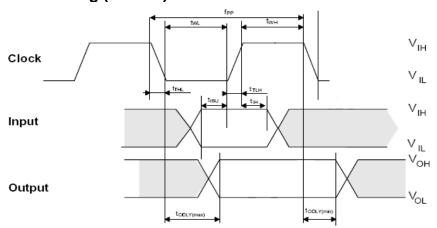

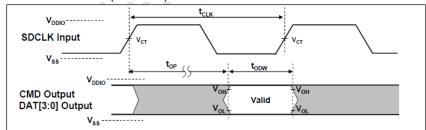

## microSD Interface timing (Default)

Shaded areas are not valid

| Parameter                                                                             | Symbol            | Min                   | Max | Unit | Remark                                |  |

|---------------------------------------------------------------------------------------|-------------------|-----------------------|-----|------|---------------------------------------|--|

| Clock CLK (All values are referred to min(V <sub>IH</sub> ) and max(V <sub>IL</sub> ) |                   |                       |     |      |                                       |  |

| Clock frequency Data Transfer Mode                                                    | f <sub>PP</sub>   | 0                     | 25  | MHz  | C <sub>card</sub> ≤ 10 pF<br>(1 card) |  |

| Clock frequency Identification Mode                                                   | f <sub>OD</sub>   | 0 <sub>(1)</sub> /100 | 400 | kHz  | C <sub>card</sub> ≤ 10 pF<br>(1 card) |  |

| Clock low time                                                                        | t <sub>WL</sub>   | 10                    |     | ns   | C <sub>card</sub> ≤ 10 pF<br>(1 card) |  |

| Clock high time                                                                       | t <sub>WH</sub>   | 10                    |     | ns   | C <sub>card</sub> ≤ 10 pF<br>(1 card) |  |

| Clock rise time                                                                       | t <sub>TLH</sub>  |                       | 10  | ns   | C <sub>card</sub> ≤ 10 pF<br>(1 card) |  |

| Clock fall time                                                                       | t <sub>THL</sub>  |                       | 10  | ns   | C <sub>card</sub> ≤ 10 pF<br>(1 card) |  |

| Inputs CMD, DAT (referenced to CLK)                                                   |                   |                       |     |      |                                       |  |

| Input set-up time                                                                     | t <sub>ISU</sub>  | 5                     |     | ns   | C <sub>card</sub> ≤ 10 pF<br>(1 card) |  |

| Input hold time                                                                       | t <sub>IH</sub>   | 5                     |     | ns   | C <sub>card</sub> ≤ 10 pF<br>(1 card) |  |

| Outputs CMD, DAT (referenced to CLK)                                                  |                   |                       |     |      |                                       |  |

| Output Delay time during Data<br>Transfer Mode                                        | t <sub>ODLY</sub> | 0                     | 14  | ns   | C <sub>L</sub> ≤ 40 pF<br>(1 card)    |  |

| Output Delay time during<br>Identification Mode                                       | tODLY             | 0                     | 50  | ns   | C <sub>L</sub> ≤ 40 pF<br>(1 card)    |  |

<sup>(1) 0</sup>Hz means to stop the clock. The given minimum frequency range is for cases were continues clock is required.

REV 0.3 Page 13 of 20 Mar. 24, 2019

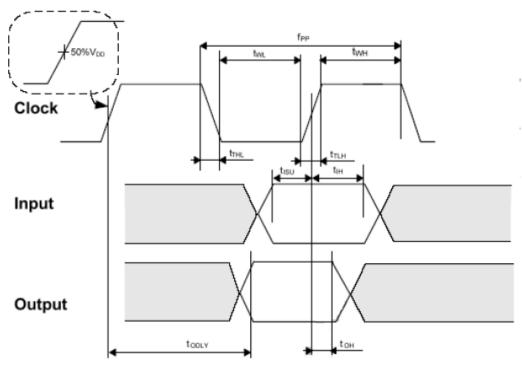

## ■ microSD Interface Timing (High-Speed Mode)

Shaded area are not valid

| Parameter                                                                             | Symbol            | Min      | Max      | Unit      | Remark                                |  |  |

|---------------------------------------------------------------------------------------|-------------------|----------|----------|-----------|---------------------------------------|--|--|

| Clock CLK (All values are referred to min(V <sub>IH</sub> ) and max(V <sub>IL</sub> ) |                   |          |          |           |                                       |  |  |

| Clock frequency Data Transfer Mode                                                    | f <sub>PP</sub>   | 0        | 50       | MHz       | C <sub>card</sub> ≤ 10 pF<br>(1 card) |  |  |

| Clock low time                                                                        | $t_{WL}$          | 7        |          | ns        | C <sub>card</sub> ≤ 10 pF<br>(1 card) |  |  |

| Clock high time                                                                       | $t_{WH}$          | 7        |          | ns        | C <sub>card</sub> ≤ 10 pF<br>(1 card) |  |  |

| Clock rise time                                                                       | t <sub>TLH</sub>  |          | 3        | ns        | C <sub>card</sub> ≤ 10 pF<br>(1 card) |  |  |

| Clock fall time                                                                       | t <sub>THL</sub>  |          | 3        | ns        | C <sub>card</sub> ≤ 10 pF<br>(1 card) |  |  |

| In                                                                                    | puts CMD,         | DAT (re  | ference  | d to CLK) |                                       |  |  |

| Input set-up time                                                                     | t <sub>ISU</sub>  | 6        |          | ns        | C <sub>card</sub> ≤ 10 pF<br>(1 card) |  |  |

| Input hold time                                                                       | t <sub>IH</sub>   | 2        |          | ns        | C <sub>card</sub> ≤ 10 pF<br>(1 card) |  |  |

| Ou                                                                                    | tputs CMD         | , DAT (r | eference | d to CLK) |                                       |  |  |

| Output Delay time during Data<br>Transfer Mode                                        | t <sub>ODLY</sub> |          | 14       | ns        | C <sub>L</sub> ≤ 40 pF<br>(1 card)    |  |  |

| Output Hold time                                                                      | T <sub>OH</sub>   | 2.5      |          | ns        | C <sub>L</sub> ≤ 15 pF<br>(1 card)    |  |  |

| Total System capacitance of each line <sup>1</sup>                                    | $C_L$             |          | 40       | pF        | C <sub>L</sub> ≤ 15 pF<br>(1 card)    |  |  |

<sup>(1)</sup> In order to satisfy severe timing, host shall drive only one card.

REV 0.3 Page 14 of 20 Mar. 24, 2019

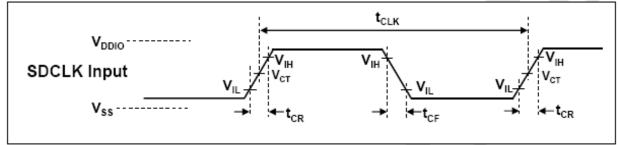

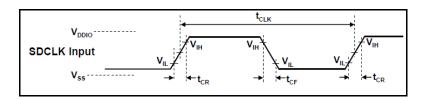

## ■ microSD Interface timing (SDR12, SDR25, SDR50 and SDR104 Modes)

Input

| Symbol     | Min  | Max        | Unit | Remark                                          |

|------------|------|------------|------|-------------------------------------------------|

| tCLK       | 4.80 | 0          | ns   | 208MHz (Max.), Between rising edge, VCT= 0.975V |

| tCR, tCF   | -    | 0.2 * tCLK | ns   | tCR, tCF < 2.00ns (max.) at 100MHz, CCARD=10pF  |

| Clock Duty | 30   | 70         | %    |                                                 |

Clock Signal Timing

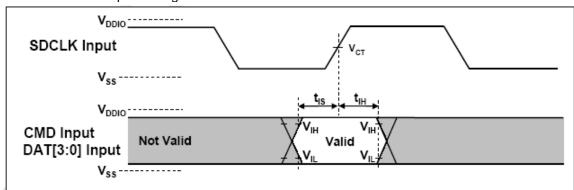

#### SDR50 and SDR104 Input Timing

| Symbol | Min  | Max | Unit | SDR104 Mode                          |

|--------|------|-----|------|--------------------------------------|

| tls    | 1.40 | -   | ns   | C <sub>CARD</sub> =10pF, VCT= 0.975V |

| tlH    | 0.80 | -   | ns   | C <sub>CARD</sub> =5pF, VCT= 0.975V  |

| Symbol | Min  | Max | Unit | SDR50 Mode                           |

| tls    | 3.00 | -   | ns   | CCARD =10pF, VCT= 0.975V             |

| tlH    | 0.80 | -   | ns   | CCARD =5pF, VCT= 0.975V              |

**Card Input Timing**

REV 0.3 Page 15 of 20 Mar. 24, 2019

#### Output Timing of Variable Window (SDR104)

| Symbol | Min  | Max   | Unit | Remark                                                |

|--------|------|-------|------|-------------------------------------------------------|

| tOP    | 0    | 2     | UI   | Card Output Phase                                     |

| ∆tOP   | -350 | +1550 | ps   | Delay variable due to temperature change after tuning |

| tODW   | 0.60 | -     | UI   | tODW=2.88ns at 208MHz                                 |

Output Timing of Fixed Data Window

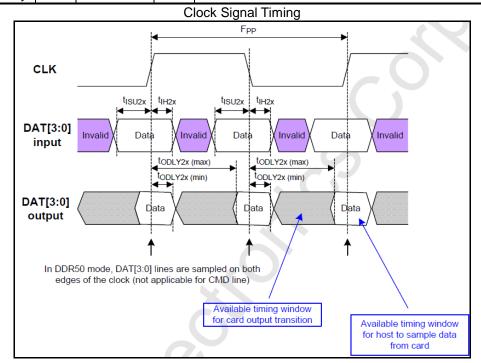

#### SD Interface timing (DDR50 Modes)

| Symbol     | Min | Max        | Unit | Remark                                        |

|------------|-----|------------|------|-----------------------------------------------|

| tCLK       | 20  | -          | ns   | 50MHz (Max.), Between rising edge             |

| tCR, tCF   | -   | 0.2 * tCLK | ns   | tCR, tCF < 4.00ns (max.) at 50MHz, CCARD=10pF |

| Clock Duty | 45  | 55         | %    |                                               |

Specifications subject to change without notice, contact your sales representatives for the most update information.

### Timing Diagram DAT Inputs / Outputs Referenced to CLK in DDR50 Mode

| Parameter                                      | Symbol              | Min      | Max        | Unit | Remark                                |  |

|------------------------------------------------|---------------------|----------|------------|------|---------------------------------------|--|

| Input CMD (referenced to CLK rising edge)      |                     |          |            |      |                                       |  |

| Input set-up time                              | t <sub>ISU</sub>    | 6        | 1          | ns   | C <sub>card</sub> ≤ 10 pF<br>(1 card) |  |

| Input hold time                                | t <sub>IH</sub>     | 0.8      | -          | ns   | C <sub>card</sub> ≤ 10 pF<br>(1 card) |  |

| Output CMD                                     | (referenced         | to CLK r | ising edge | )    |                                       |  |

| Output Delay time during Data<br>Transfer Mode | t <sub>ODLY</sub>   |          | 13.7       | ns   | C <sub>card</sub> ≤ 30 pF<br>(1 card) |  |

| Output Hold time                               | t <sub>OH</sub>     | 1.5      | -          | ns   | C <sub>card</sub> ≤ 10 pF<br>(1 card) |  |

| Inputs DAT (refere                             | edges)              |          |            |      |                                       |  |

| Input set-up time                              | t <sub>ISU2X</sub>  | 3        | -          | ns   | C <sub>card</sub> ≤ 10 pF<br>(1 card) |  |

| Input hold time                                | t <sub>IH2X</sub>   | 0.8      | -          | ns   | C <sub>card</sub> ≤ 10 pF<br>(1 card) |  |

| Outputs CMD, DAT (referenced to CLK)           |                     |          |            |      |                                       |  |

| Output Delay time during Data<br>Transfer Mode | t <sub>ODLY2X</sub> | -        | 7.0        | ns   | C <sub>L</sub> ≤ 25 pF<br>(1 card)    |  |

| Output Hold time                               | t <sub>OH2X</sub>   | 1.5      | -          | ns   | C <sub>L</sub> ≥ 15 pF<br>(1 card)    |  |

REV 0.3 Page 17 of 20 Mar. 24, 2019

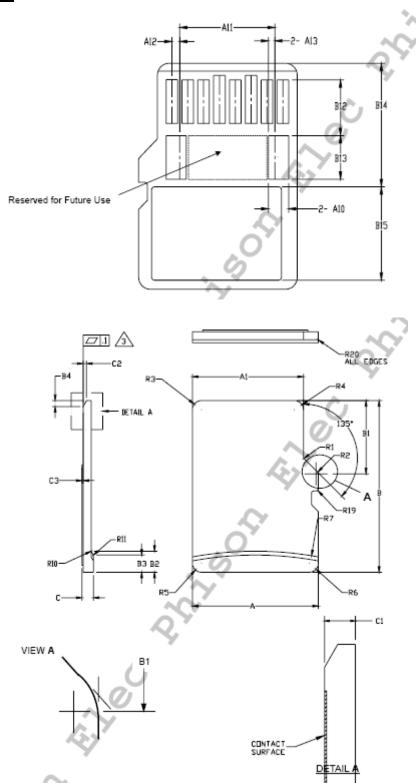

## 10. <u>Dimensions</u>

REV 0.3 Page 18 of 20 Mar. 24, 2019

|            | COMMON | DIMENS | IIONS:  |          |

|------------|--------|--------|---------|----------|

| SYMBOL     | MIN    | NOM    | MAX     | NOTE     |

| A          | 10.90  | 11.00  | 11.10   | PROTE    |

| A1         | 9.60   | 9.70   | 9.80    |          |

| A2         | 3.00   | 3.85   | 5,00    | BASIC    |

| A3         | 7.60   | 7.70   | 7.80    | UPOIG    |

| A4         | 7.00   | 1.10   | 7.00    | BASIC    |

|            | 0.75   |        |         | DMOIL    |

| A5         | 0.75   | 0.80   | 0.85    |          |

| A6         | -      | -      | 8.50    |          |

| AZ         | 0.90   |        |         |          |

| A8         | 0.60   | 0.70   | 0.80    |          |

| A9         | 0.80   |        |         |          |

| A10        | 1.35   | 1.40   | 1.45    |          |

| A11        | 6.50   | 6.60   | 6.70    |          |

| A12        | 0.50   | 0.55   | 0.60    |          |

| A13        | 0.40   | 0.45   | 0.50    |          |

| В          | 14.90  | 15.00  | 15.10   |          |

| B1         | 6.30   | 6.40   | 6.50    |          |

| B2         | 1.64   | 1.84   | 2.04    |          |

| B3         | 1.30   | 1.50   | 1.70    |          |

| B4         | 0.42   | 0.52   | 0.62    |          |

| B5         | 2.80   | 2.90   | 3.00    |          |

| B6         | 5.50   | -      | -       |          |

| B7         | 0.20   | 0.30   | 0.40    |          |

| B8         | 1.00   | 1.10   | 1.20    |          |

| E9         | -      | - 12   | 9.00    |          |

| B10        | 7.80   | 7.90   | 8.00    |          |

| B11        | 1.10   | 1.20   | 1.30    |          |

|            |        |        |         |          |

| B12        | 3.60   | 3.70   | 3.80    |          |

| B13        | 2.80   | 2.90   | 3.00    |          |

| B14<br>B15 | 8.20   | -      | 6.20    |          |

|            | 0.00   | 4.00   |         |          |

| C          | 0.90   | 1.00   | 1.10    |          |

| C1         | 0.60   | 0.70   | 0.80    | $\neg$   |

| C2         | 0.20   | 0.30   | 0.40    | <u> </u> |

| C3         | 0.00   | -      | 0.15    |          |

| D1         | 1.00   | -      | -       |          |

| D2         | 1.00   | _      | -       |          |

| D3         | 1.00   | - (    | -       |          |

| R1         | 0.20   | 0.40   | 0.60    |          |

| R2         | 0.20   | 0.40   | 0.60    |          |

| R3         | 0.70   | 0.80   | 0.90    |          |

| R4         | 0.70   | 0.80   | 0.90    |          |

| R5         | £70    | 0.80   | 0.90    |          |

| R6         | 0.70   | 0.80   | 0.90    |          |

| R7         | 29.50  | 30.00  | 30.50   |          |

| R10        | 77     | 0.20   | -       |          |

| R11        | -      | 0.20   | -       |          |

| R17        | 0.10   | 0.20   | 0.30    |          |

| R18        | 0.20   | 0.40   | 0.60    |          |

| R19        | 0.05   | -      | 0.20    |          |

| R20        | 0.02   | _      | 0.15    |          |

| 100        | 10.456 | _      | Co. No. |          |

#### Notes:

- DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- 2. DIMENSIONS ARE IN MILLIMETERS.

- COPLANARITY IS ADDITIVE TO C1 MAX THICKNESS.

## **Appendix: Part Number Table**

## SLC

| Product                          | Advantech PN       |

|----------------------------------|--------------------|

| SQF MICRO SD SLC 128M (-25~85°C) | SQF-MSDS1-128M-21C |

| SQF MICRO SD SLC 256M (-25~85°C) | SQF-MSDS1-256M-21C |

| SQF MICRO SD SLC 512M (-25~85°C) | SQF-MSDS1-512M-21C |

| SQF MICRO SD SLC 1G (-25~85°C)   | SQF-MSDS1-1G-21C   |

| SQF MICRO SD SLC 2G (-25~85°C)   | SQF-MSDS1-2G-21C   |

| SQF MICRO SD SLC 4G (-25~85°C)   | SQF-MSDS1-4G-21C   |

| SQF MICRO SD SLC 128M (-40~85°C) | SQF-MSDS1-128M-21E |

| SQF MICRO SD SLC 256M (-40~85°C) | SQF-MSDS1-256M-21E |

| SQF MICRO SD SLC 512M (-40~85°C) | SQF-MSDS1-512M-21E |

| SQF MICRO SD SLC 1G (-40~85°C)   | SQF-MSDS1-1G-21E   |

| SQF MICRO SD SLC 2G (-40~85°C)   | SQF-MSDS1-2G-21E   |

| SQF MICRO SD SLC 4G (-40~85°C)   | SQF-MSDS1-4G-21E   |

REV 0.3 Page 20 of 20 Mar. 24, 2019